FPGAs for the FIX community: Bridging the gap between hardware & software

nxFramework FIX engine offers scalable way to handle large volumes of FIX traffic while reducing server footprint

The FIX® Protocol is a market standard for electronic messaging, facilitating the exchange of market data and trade information between financial entities, such as investment banks, trading platforms and broker-dealers.

However, due to its use of ASCII, variable data structures and large datagrams, processing large volumes of FIX traffic represents a challenge for standard CPU-based architectures, which remains the industry norm.

The launch of FIX protocol support for nxFramework, an FPGA-based development framework, directly tackles the issue facing users who struggle to process FIX messages efficiently. The addition of our industry-first, FPGA FIX engine, offloads the management of hundreds of sessions to the FPGA while using only two CPU cores – a task that typically requires up to 40 CPU cores dedicated to only FIX protocol processing.

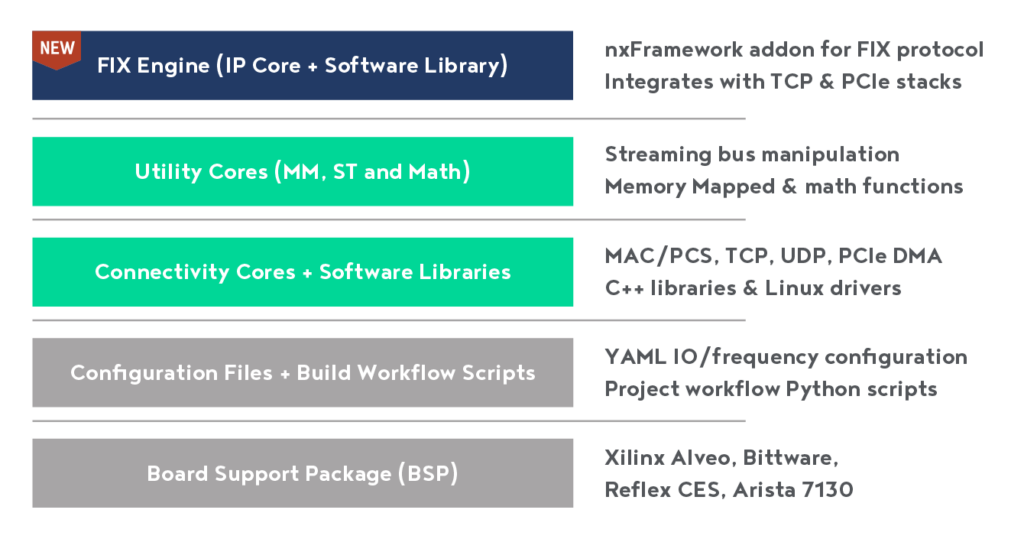

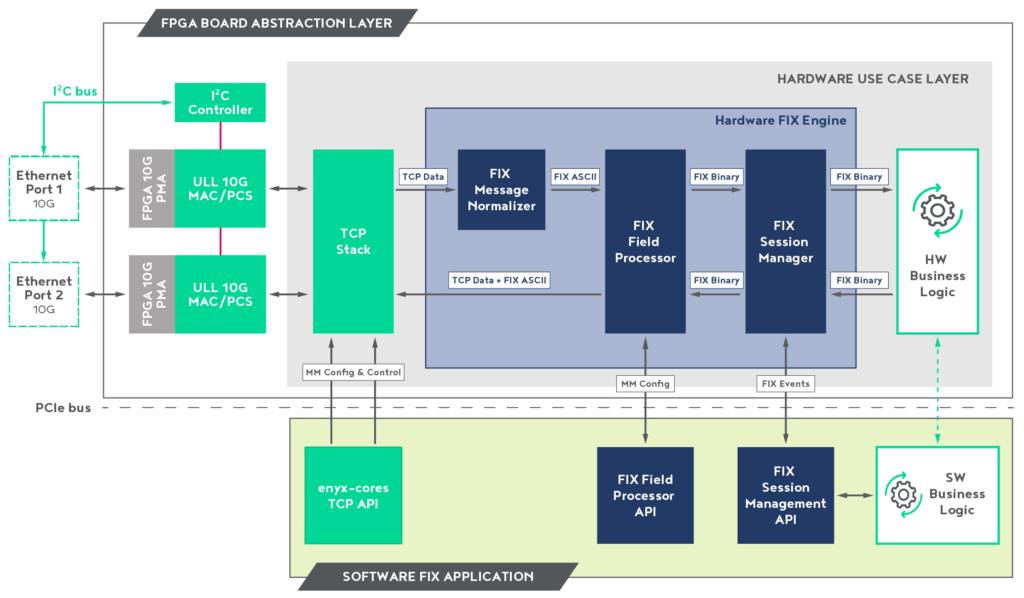

Standard nxFramework stack with addition of the FIX engine. The FIX engine integrates with the nxFramework TCP & PCIe stacks

Bridging the gap between hardware and software by offering a flexible, software-configurable FIX stack running on hardware

The nxFramework FIX offload engine offers several advantages:

- Data Transcoding: Our FPGA card serves as a versatile network card, capable of transcoding the FIX 4.4 ASCII protocol into binary format and vice versa. This transformation facilitates the manipulation of data streams in a deterministic and low latency manner.

- Data Processing: Within nxFramework, users can swiftly embed their business logic directly into the data path. This allows users to modify data content on the fly and retransmit altered FIX messages without exiting the FPGA, across numerous sessions.

- Compute Density: With the ability to execute FIX gateways, pre-trade risk assessments, FIX to native, and native to FIX processes all directly on the FPGA – users can lower latency while conserving valuable CPU cycles – reducing power consumption, and ultimately lowering operational costs.

Beyond hardware implementation: A comprehensive set of software libraries

The nxFramework software libraries are designed to configure, monitor, and support the IP cores – allowing for seamless integration with existing infrastructure and lowering time-to-production.

Fully managed in software, users can control the TCP stack, configure the FIX engine, and handle the FIX sessions via simple, dedicated C++ APIs. Clients without internal FPGA resources can still benefit from the processing power of FPGA technology.

By using pre-configured templates to validate FIX messages, nxFramework FIX engine can filter out unnecessary data. This allows for significant processing to be offloaded from software to the FPGA – ensuring that only necessary computational resources are utilized for mission critical tasks.

The nxFramework runtime software stack includes the addition of FIX engine software libraries.

Why is this important for the FIX community? Don’t reinvent the wheel.

The addition of the FIX engine to nxFramework unlocks the power of FPGA for the FIX community.

The FIX engine gives users the ability to receive, transmit, and process FIX sessions directly from the FPGA in a deterministic fashion. This enables existing servers to be easily upgraded with FPGA smart NICs, capable of offloading the processing of FIX protocol – freeing up CPU resources, improving compute density and reducing total cost of ownership.

Furthermore, for more latency-sensitive use cases, nxFramework can be used to develop and deploy custom FPGA firmware for embedding critical business logic, in addition to the FIX protocol processing.

As a mature, standardized FPGA development framework, the solution offers a complete set of libraries and tools required for building high performance applications – allowing users to utilize their valuable time and resources more effectively.

Typical Use Cases

Exchanges & Service Providers

- Order execution gateway processing participant orders (FIX to Binary)

- Full FPGA FIX gateway (bump in the wire)

- Business logic on the FPGA

- Publication of market data over FIX for end-user convenience

- Generic protocol processing offload (Binary to FIX)

- Accelerator type deployment with business logic on software

Prime Brokerage

- FIX to native pre-trade risk check gateways for low latency sponsored access

Technical Overview

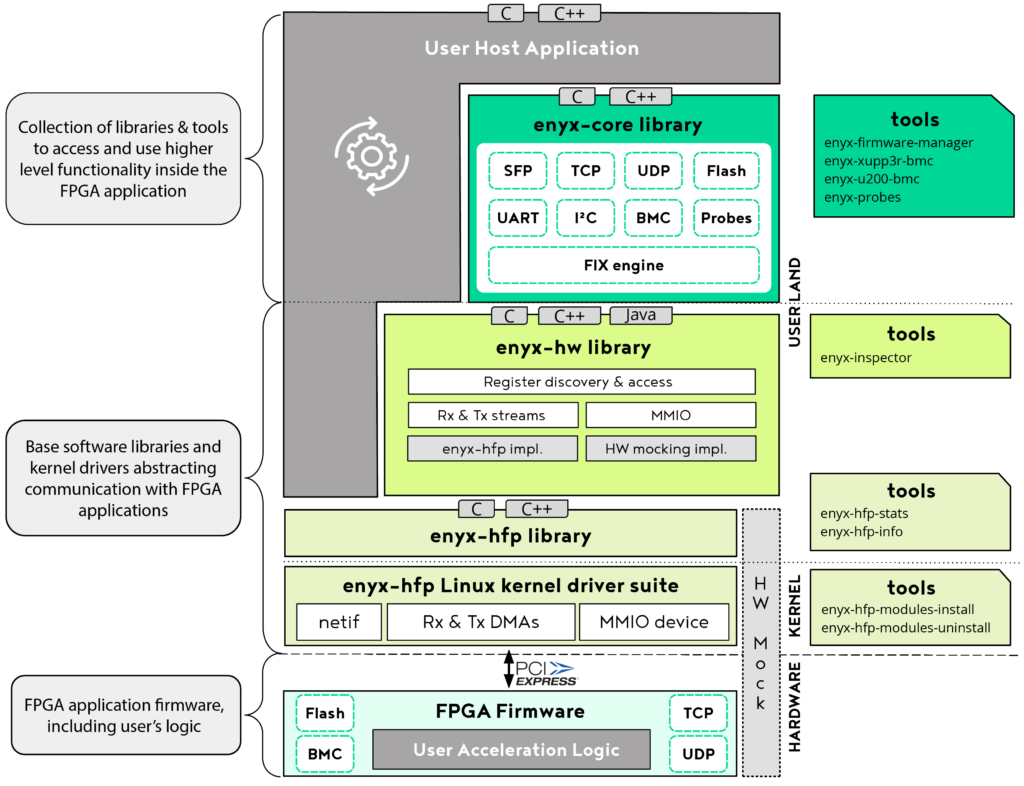

nxFramework block diagram highlighting the integration of the FIX engine with software and hardware business logic

FIX Field Processor

- Decode pre-defined fields, configurable at runtime

- Configuration-based ASCII/Binary conversion

FIX Session Manager

- Manage up to 128 sessions

- Check and insert CompIDs

- Maintain FIX connection and sequence mapping

- Forward FIX administration messages to the host software

nxFramework software libraries

- FIX engine API: A software library that controls and monitors the FIX engine, in addition to managing FIX administration messages

- enyx-hw: A multilayer software library that provides all communication primitives to interact with an FPGA accelerator through abstracted interfaces for packet streaming and memory input/output

- enyx-cores: A software library that relies on enyx-hw for accelerator communication and provides higher level methods to configure, monitor and use the hardware IP cores that are part of nxFramework such as:

- TCP and UDP networking stacks

- Flash management

- Board Management Controller (temperature, hardware health status)

- I²C and UART MMIO bridge primitives